## **INDICE DE LA PRACTICA**

### **INTRODUCCIÓN.**

- **CARACTERISTICAS DE LA PRACTICA**

- **ANÁLISIS DE AMPLIFICADORES DIFERENCIALES BÁSICOS.**

- **ETAPA DE AMPLIFICADOR DIFERENCIAL.**

- **MODOS DE TRABAJO DE UN AMPLIFICADOR DIFERENCIAL.**

- **ANALISIS DEL AMPLIFICADOR DIFERENCIAL EN MODO DE PEQUEÑA SEÑAL.**

- **PROBLEMATICA DE DISEÑO**

- **POLARIZACIÓN POR ESPEJO DE CORRIENTE, CONFIGURACIÓN WILSON.**

- **LIMITACIONES DE POTENCIA.**

- **CÁLCULOS PARA LA GANANCIA Y DETERMINACIÓN DEL PUNTO DE TRABAJO.**

- **CÁLCULO DE AMD.**

- **CÁLCULO DE I, RC, RX.**

- **SIMULACIÓN CON PSPICE.**

- **ESQUEMA DE NODOS.**

- **FICHERO .CIR**

- **FICHERO .OUT**

- **GRAFICAS.**

- **DOCUMENTACIÓN TÉCNICA.**

- **BIBLIOGRAFÍA.**

### **INTRODUCCIÓN.**

En este apartado se indican las características que debe presentar la práctica que a continuación se realiza, así como una breve descripción de las características y configuraciones.

- **CARACTERISTICAS DE LA PRÁCTICA.**

Se trata de diseñar un **AMPLIFICADOR DIFERENCIAL** de baja frecuencia haciendo uso de componentes discretos.

El Amplificador ha de cumplir las siguientes especificaciones:

- La salida se tomará entre el colector de uno de los transistores y tierra ( $V_o$ ).

- La entrada se tomará de un generador senoidal ( $V_i$ ) insertado entre la base de un transistor y tierra ( $V_i$ ), estando la otra base directamente unida a tierra.

- Ganancia de tensión ( $V_o/V_i$ )  $>45$  dB.

- CMRR (Relación de rechazo en modo común)  $>50$  dB.

- Disponemos de alimentación del circuito de generadores de corriente continua de 12 voltios.

### **2.) ANÁLISIS DE AMPLIFICADORES DIFERENCIALES BÁSICOS**

El *Amplificador Diferencial, par de emisor acoplado, o par diferencial* es un bloque constructivo esencial en los modernos amplificadores integrados.

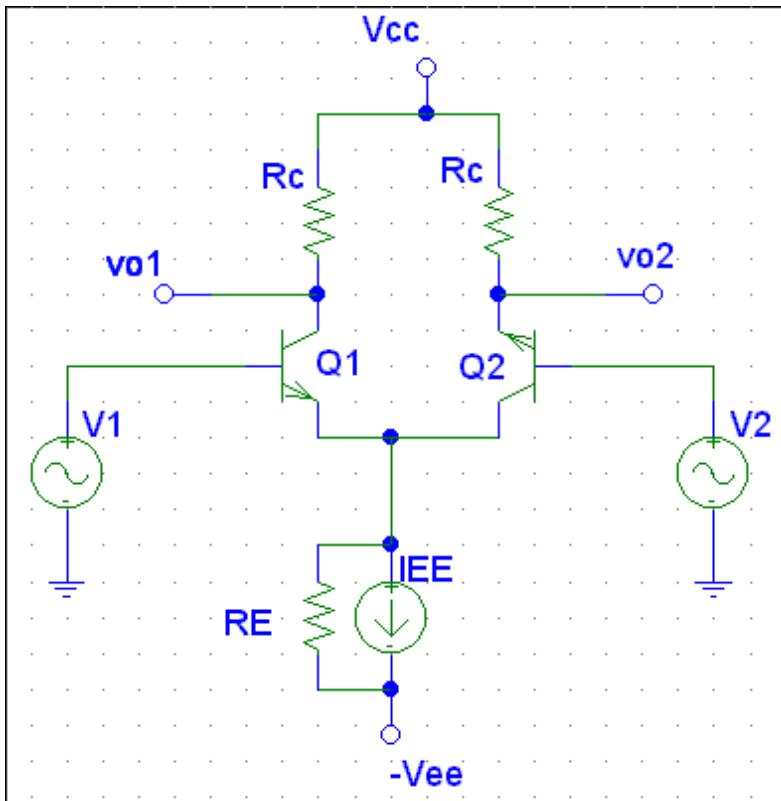

El esquema general de este circuito es el que a continuación se indica.

En este circuito se diferencian dos etapas distintas:

- Una formada por el amplificador diferencial propiamente dicho donde aparece la fuente de señal y los transistores enfrentados con las redes de polarización

- Otra formada por una fuente de corriente real (con resistencia en paralelo a la fuente).

A continuación se definen ambas etapas.

### **2.1.) ETAPA DE AMPLIFICACIÓN DIFERENCIAL.**

El Amplificador diferencial se caracteriza por presentar dos transistores idénticos con similares características, tanto internas como de las redes de polarización.

Ya que el circuito dispone dos entradas y dos salidas de señal, existen cuatro configuraciones posibles realizando las distintas combinaciones entre entradas y salida.

- **Entrada y salida simétrica:** Es la forma más típica de un amplificador diferencial, tiene dos entradas v1 y v2, El voltaje de salida se obtiene de la diferencia entre las salidas de los colectores.

- **Entrada asimétrica y salida simétrica:** En algunas aplicaciones sólo se usa uno de los terminales de entrada con la otra conectada a tierra, mientras que la salida se obtiene entre los colectores de los dos transistores del circuito.

- **Entrada simétrica y salida asimétrica:** Esta es la forma más práctica y utilizada porque puede excitar cargas asimétricas o de un solo terminal como lo hacen los amplificadores EC, emisor seguidor y otros circuitos. Esta etapa es la que se usa para la etapa de entrada de la mayor parte de los Amplificadores Operacionales comerciales. Presenta dos entradas de señal para las bases de cada transistor mientras que la salida se obtiene únicamente de uno de los colectores respecto a masa

- **Entrada y salida asimétrica:** Esta configuración presenta tanto para la entrada como para la salida un único terminal. Este tipo de configuración es útil para las etapas de acoplamiento directo donde se requiere sólo amplificar una entrada. **Esta configuración es la que se solicita en las especificaciones**

de la práctica.

### 2.1.1) Modos De Trabajo De Un Amplificador Diferencial.

**Modo Diferencial:** Para  $V1=V2$  y suponiendo  $F \gg 1$ , las corrientes de colector y emisor de cada etapa son iguales. Todas estas corrientes tienen magnitudes iguales (aproximadamente) a  $IE/2$  debido a la simetría del circuito y a la despreciable corriente que circula por  $RE$ . Si incrementamos  $V1$  en  $v/2$  y simultáneamente disminuimos  $V2$  en  $v/2$ , la señal de salida aumenta en  $v$  advertir que el circuito funciona en modo lineal mientras  $v < 4VT$ .

**Modo Común:** Consideremos que las dos tensiones  $V1$  y  $V2$  aumentan en  $v/2$ . La tensión diferencial  $Vd$  permanece nula mientras que  $Ic1$  e  $Ic2$  son iguales. No obstante la tensión  $VE$  aumenta.

Por lo tanto dependiendo de la señal de entrada, el amplificador diferencial actúa o bien como etapa en emisor común o bien como etapa en emisor común con resistencia de emisor. Por lo tanto la ganancia de esta etapa es notablemente mayor en el funcionamiento como modo diferencial que como modo común. Normalmente los amplificadores diferenciales se diseñan de forma que a efectos prácticos sólo resulten amplificadas las señales diferenciales.

### 2.1.2.) Análisis De Amplificador Diferencial En Pequeña Señal.

Explicadas los distintos tipos de un amplificador diferencial, pasamos a continuación a un estudio más detallado de los conceptos importantes de las ganancias.

A continuación se definen los conceptos más importantes, tales como **Ganancia ADM del modo diferencial**, **Ganancia ACM del modo Común** y la **Relación de Rechazo del Modo Común CMRR**.

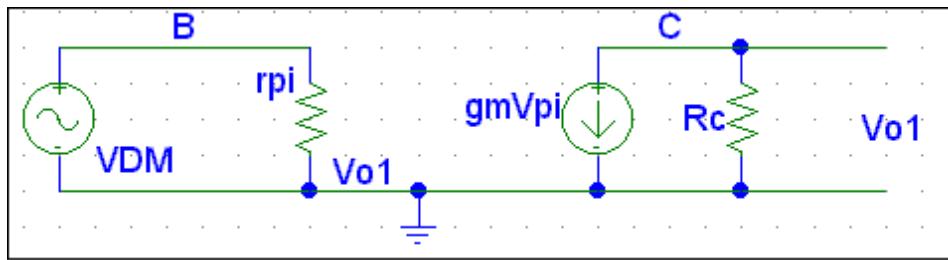

- **Ganancia del modo diferencial:** Consideremos que se aplica una señal  $VDM$  a la base de  $Q1$ . Empleando el concepto de semi-circuito, es decir analizando sólo una mitad del circuito, se llega al modelo de pequeña señal de la figura siguiente.

Con  $VDM$  positivo,  $Vo1 = ADM * VDM$ . Si queremos que las señales de entrada y salida se encuentran en fase, sedemos tomar obtener la salida por el transistor opuesto al que se introduce la señal, es decir si la fuente de señal se coloca en la base de  $Q1$ , la salida se deberá sacar del colector de  $Q2$  para que ambas señales estén en fase.

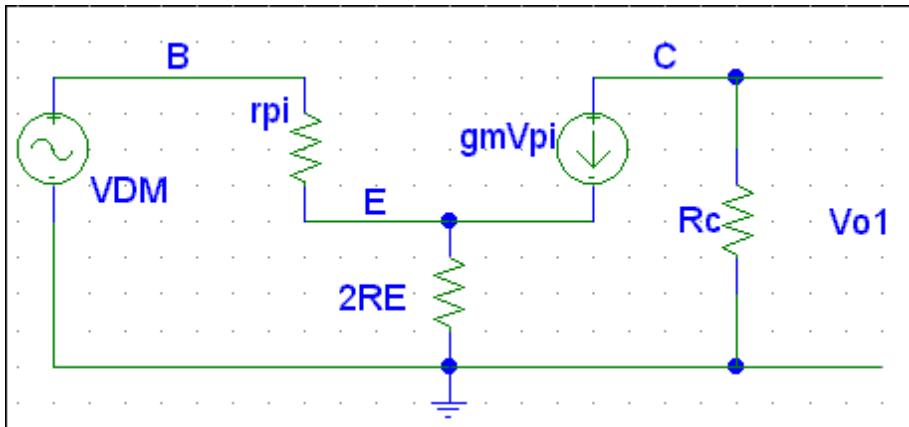

- **Ganancia del modo común:** Una señal en modo común es aquella que se aplica simultáneamente a las dos entradas del Amplificador Diferencial. La mayor parte de las señales de interferencia, estática y otro tipo de señales indeseables son señales en modo común. Lo que ocurre es que los cables conectados a las bases de entrada actúan como pequeñas antenas; si el A.D. está operando en un ambiente con interferencias electromagnéticas, ambas bases capturan la misma señal. Una de las razones de la popularidad de los amplificadores diferenciales es que discriminan las señales de modo común. En otras palabras, un amplificador diferencial no amplifica señales de modo común, evitando de esa forma tener a la salida señales indeseables. Ahora veremos porqué un Amplificador diferencial

no amplifica señales en modo común. Cuando se aplica una señal VCM,  $V_d=0$  a ambas bases, es válido el circuito que a continuación se indica.

Para este circuito la ganancia ACM será:

El significado es claro, cuando una señal en modo excita el amplificador, aparece una gran resistencia de emisor en el circuito equivalente de c.a.

- **Razón de rechazo del modo común:** En un principio el amplificador diferencial se diseña para amplificar señales diferenciales; por lo tanto se requiere que  $ADM \gg ACM$ . Una forma de valorar la actuación de un transistor es mediante la relación de rechazo al modo común, que queda definida de la siguiente forma:

Como puede desprenderse de lo anteriormente indicado, para obtener unos valores mínimamente aceptables, algunos textos y catálogos establecen 72 dB de CMRR como mínimo aceptable, se requiere grandes valores de RE y frecuentemente se necesita emplear fuentes de corrientes con resistencias de salidas altas.

Para aumentar el CMRR se debe aumentar la tensión Early efectiva, es decir, la resistencia de salida de la fuente de corriente. Los A.O. con relaciones de rechazo del modo común comprendidas entre 80 y 90 dB emplean por lo general fuentes de corrientes Wilson, Widar o Cascodo.

## 2.2. PROBLEMATICA DE DISEÑO.

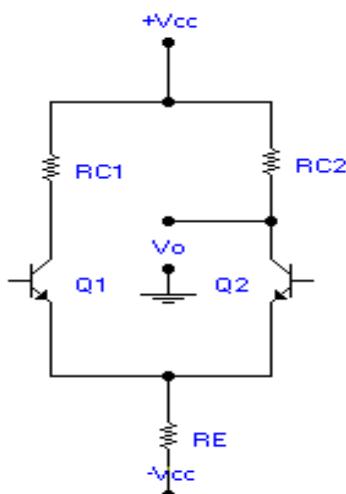

En este punto del diseño de la práctica nos encontramos el primer problema de diseño. Con el esquema que a continuación se indica, se necesitaría una RE muy grande (como se ha indicado anteriormente) para obtener el valor del CMRR solicitado en las especificaciones de la práctica.

El problema que nos encontramos es que si aumentamos excesivamente la RE para obtener una mejor Razón de rechazo del modo común, aumentamos la pendiente de la recta de carga en alterna con lo que la señal de salida puede sufrir recortes en los picos al entrar en zona de corte o saturación.

Se opta pues por una fuente de corriente dispuesta en configuración de espejo de corriente y que disponga de una elevada resistencia de salida, mucho más alta de la que se podría obtener con una polarización de emisor convencional.

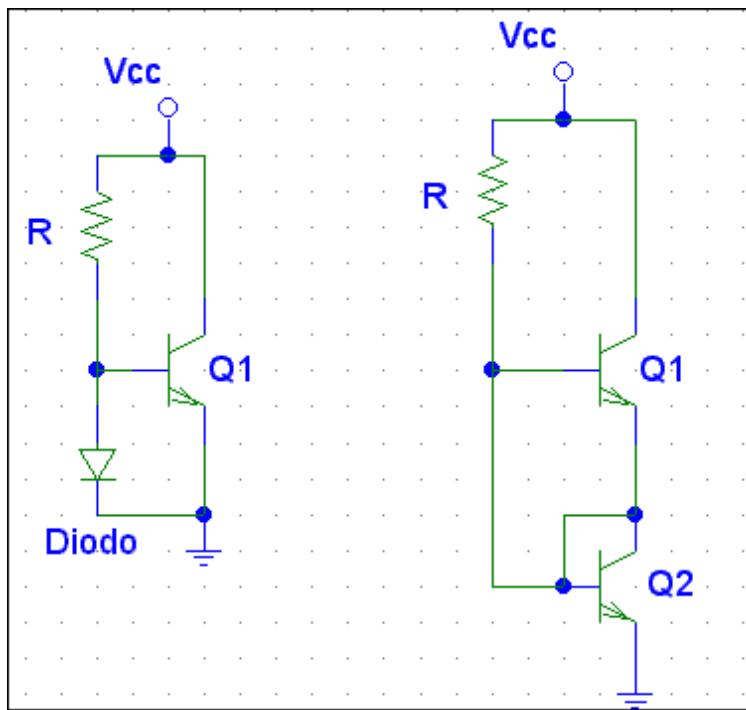

### **2.3. POLARIZACIÓN POR ESPEJO DE CORRIENTE.**

La polarización por espejo de corriente se basa en que la corriente de base es mucho más pequeña que la corriente de la resistencia y por el diodo, por lo que la corriente por la resistencia y por el diodo son prácticamente iguales. Si la curva del diodo fuese idéntica a la curva de VBE del transistor, la corriente del diodo sería igual a la corriente de emisor y se llegaría a la siguiente conclusión: que la corriente del colector es aproximadamente igual a la corriente que circula a través de la resistencia de polarización. Este circuito es muy importante, ya que significa que se puede fijar la corriente de colector al controlar la corriente de la resistencia. El circuito se comporta entonces como un espejo, la corriente de la resistencia se refleja en el colector del transistor.

Explicado el concepto básico de funcionamiento de este tipo de circuitos, generalmente no se colocan diodos, ya que las características de recta de carga del diodo y el diodo Base–Emisor del transistor difieren. Es por esto por lo que se usan dos transistores de idénticas características, uniendo en uno de ellos la base y el colector consiguiendo de esta forma un diodo.

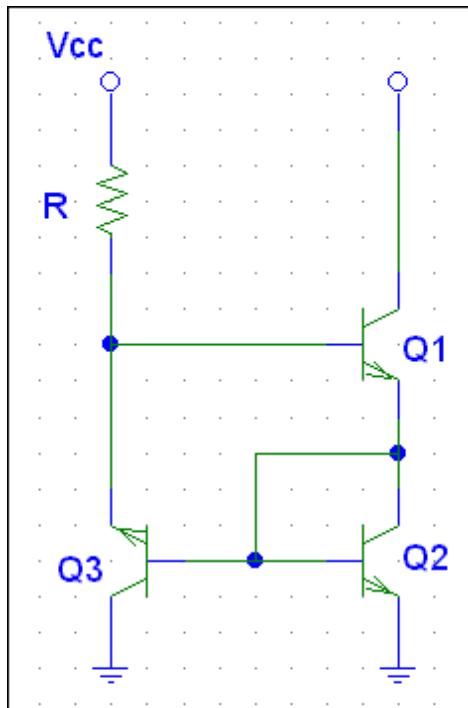

Para la realización del circuito de polarización de espejo de corriente hemos optado por la configuración de fuente de corriente de tres transistores Wilson por ser una etapa de alta impedancia y por la diferencia tan extremadamente pequeña entre la corriente de colector y IRC como se verá más adelante.

El esquema de esta disposición es la siguiente.

La corriente de la fuente  $I_c$  puede expresarse de la siguiente forma:

Quedando la diferencia en

Evidentemente esta diferencia es extremadamente pequeña para cualquier valor modesto de  $F$ . Además la resistencia de salida de una fuente Wilson es mayor que  $r_0$  de  $Q1$  ya que el transistor  $Q3$  conectado como diodo actúa como resistencia de emisor.

### **3. LIMITACIONES DE POTENCIA.**

Tendremos que considerar un factor importante a la hora de ver nuestras limitaciones en el diseño, es decir, tendremos que determinar el conjunto de valores  $(V, I)$  con que vamos a polarizar los transistores sin que estos se destruyan, por lo tanto tendremos que analizar toda la circuitería.

Nosotros trabajaremos con transistores NPN tipo Q2N2222A cuyas características técnicas se indican al final de la memoria. La potencia máxima que puede disipar de 500mW, sin embargo, por razones de seguridad nosotros situaremos el máximo de potencia en 250mW.

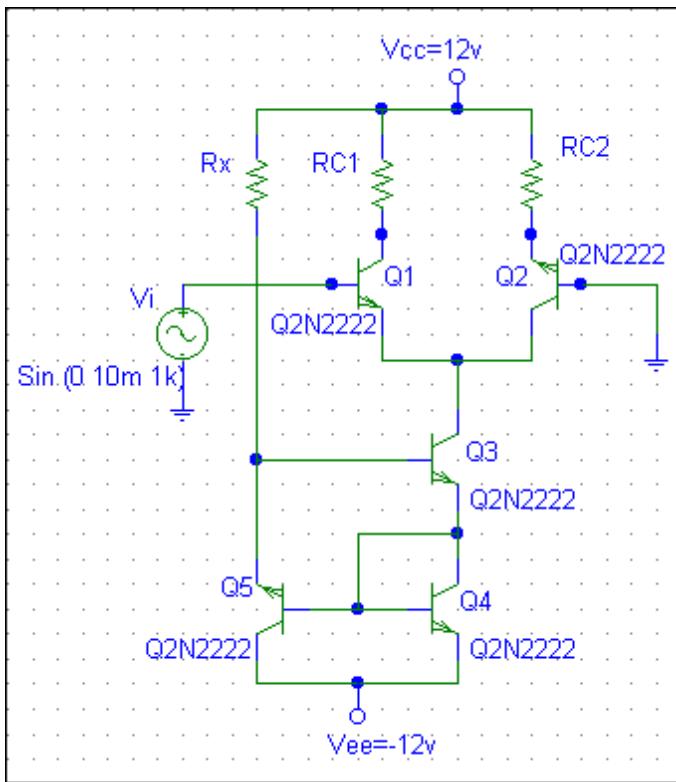

Pasaremos al estudio del circuito completo de la práctica cuyo esquema es el siguiente:

Parece claro que para que los dos transistores Q4 y Q5 estén en activa se debe cumplir que  $V_{Q3} = -0,7$  voltios =  $V_E$  Q1 ó Q2. A su vez para que todos los transistores conduzcan tiene que ocurrir que  $V_{be} = 0,7$  voltios y también que  $I_x = I$ , teniendo esto en cuenta pasaremos a hallar los voltajes  $V_{ce}$  de todos los transistores y a su vez cual es la intensidad máxima que puede circulara través de ellos. Teniendo en cuenta todo esto, tenemos que siendo:

$V_{EE} = -12$  voltios y  $V_{cc} = 12$  voltios se cumple:

, de aquí obtenemos

, por lo tanto

Por lo tanto para que el transistor que más nos limita el valor de la intensidad es Q3, para el que a continuación se realizan los siguientes cálculos:

Por lo que la intensidad de fuente nunca deberá pasar de este valor.

En los transistores del diferencial, es decir, Q1 y Q2 tendremos garantizados la no destrucción por exceso de potencia porque y a través de ellos pasa un máximo de corriente con valor , y  $V_{CE}$  nunca llegará a los 10 voltios.

#### **4. CÁLCULOS PARA LA GANANCIA Y DETERMINACIÓN DEL PUNTO DE TRABAJO.**

Determinaremos en este apartado las ecuaciones de la ganancia y el punto de polarización.

En el amplificador diferencial la salida se toma desde uno de los colectores respecto a tierra por lo tanto la ganancia tendrá la siguiente expresión:

Veremos de qué depende el producto  $I_{rc}$ , para lo que haremos aplicación de las Leyes de Kirchhoff y en la

malla de salida tendremos:

---

y sustituyendo en la expresión de la ganancia:

En este caso se ve claramente que la ganancia depende del valor VCE. Ahora si tenemos en cuenta que el valor VCE debe ser tal que permita la máxima excursión de la señal y como la recta de carga en continua y alterna coincide tendremos que  $VCE=6$  voltios.

#### **4.1. CALCULO DE GANANCIA EN MODO DIFERENCIAL ADM**

Comprobamos ahora si con este valor de VCE se cumple que  $AMD>45$  dB.

Sin embargo con  $VCE = 6$  voltios obtenemos una ganancia AMD de 40dB. Este valor está por debajo de lo que se solicita en la práctica, por lo tanto tenemos que bajar el valor mínimo de VCE hasta obtener una AMD  $>45$  dB.

Evidentemente este valor de VCE nos va a desplazar el punto de trabajo óptimo, sin embargo esta es una condición sin la cual no obtendremos la amplificación requerida en las especificaciones.

Para la práctica establecemos una valor de  $VCE=2.8$  voltios, obteniendo así una ganancia , cumpliendo las especificaciones requeridas en la práctica.

#### **4.2 CALCULO DE I, Rc y Rx.**

Fijaremos la corriente de fuente a un valor  $I=10$  mA, por lo tanto nos queda hallar el valor de Rx que haga circular esta corriente.

Aplicando la ecuación de malla

Por lo tanto  $Rc$  ya es fácil de calcular.

El factor de rechazo de modo común se ha supuesto infinito y en circuito real casi no se puede medir.

#### **5. SIMULACIÓN CON PSPICE.**

A continuación se aportan los datos que el programa de simulación PSPICE aporta en la práctica.

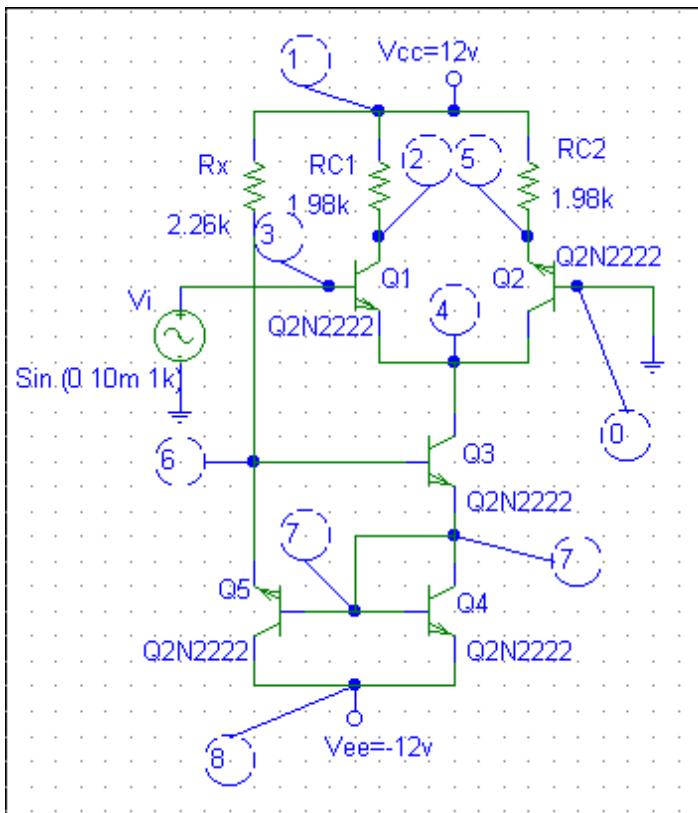

#### **5.1. ESQUEMA CON DEFINICIÓN DE NODOS.**

En el esquema se muestra el circuito final con los valores de las resistencias anteriormente calculados y la denominación de cada uno de los nodos que posteriormente se indican en el listado del fichero .CIR de PSPICE.

## **5.2. FICHERO .CIR**

AMPLIFICADOR DIFERENCIAL CON ENTRADA Y SALIDA ASIMETRICA

VCC 1 0 12

VEE 0 8 12

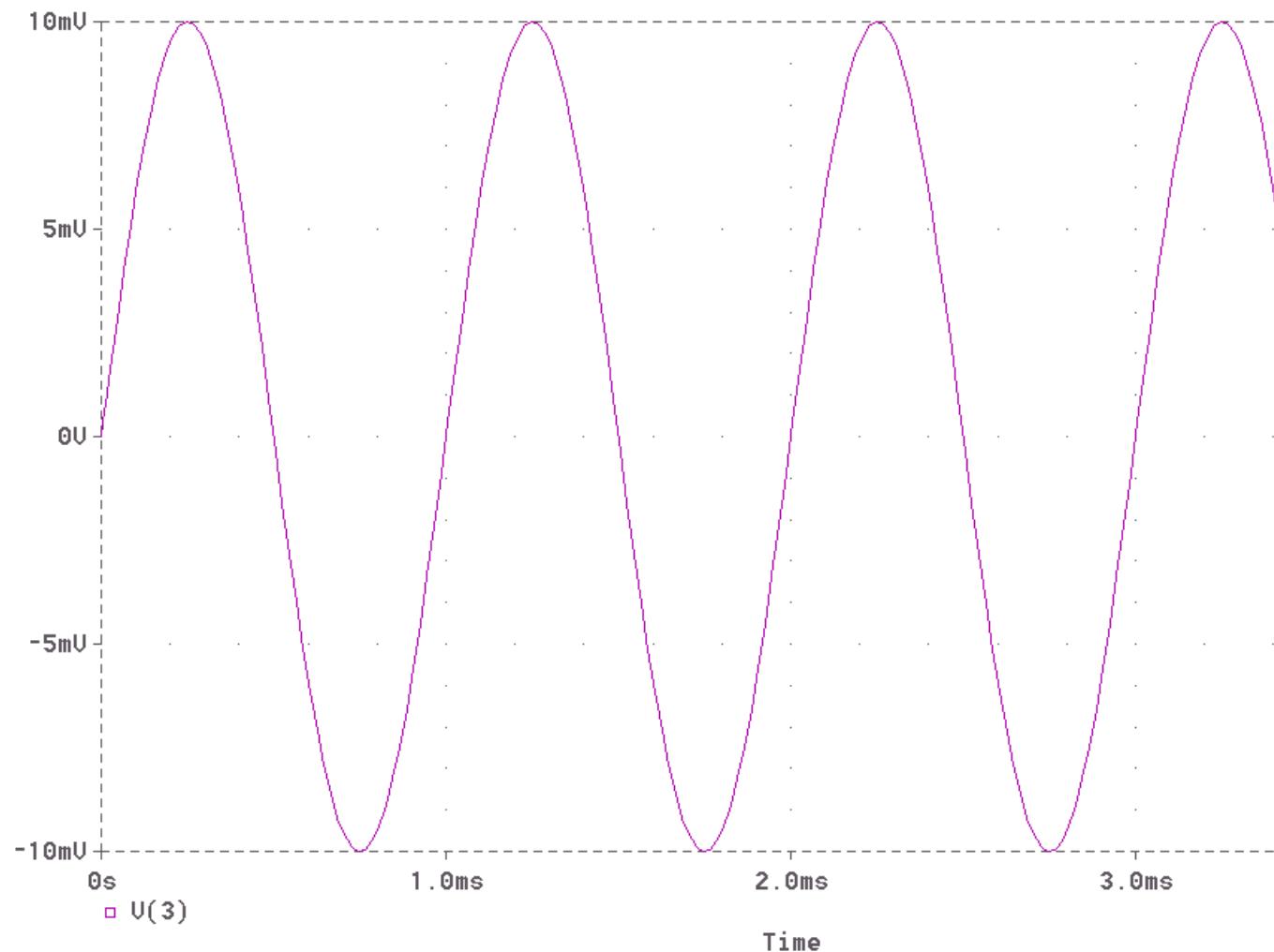

$V_1$  3 0  $\text{SIN}(0 10\text{M} 1\text{k})$

RC1 1 2 1.98K

RC2 1 5 1.98K

Q1 2 3 4 Q2N2222

Q2 5 0 4 Q2N2222

Q3 4 6 7 Q2N2222

Q4 7 7 8 Q2N2222

Q5 6 7 8 Q2N2222

RX 1 6 2.26K

.MODEL Q2N2222 NPN (BF=191 IS=4E-15)

.LIB C:\PS8\LIB\BIPOLAR.LIB

.TRAN/OP 1.000U 4M 0 20U

.PROBE

.END

### **5.3.Fichero .OUT**

\*\*\*\* 01/17/2000 03:53:35 \*\*\*\*\* NT Evaluation PSpice (July 1997) \*\*\*\*\*

AMPLIFICADOR DIFERENCIAL CON ENTRADA Y SALIDA ASIMETRICA

\*\*\*\* CIRCUIT DESCRIPTION

\*\*\*\*\*

VCC 1 0 12

VEE 0 8 12

Vi 3 0 SIN(0 10M 1K)

RC1 1 2 1.98K

RC2 1 5 1.98K

Q1 2 3 4 Q2N2222

Q2 5 0 4 Q2N2222

Q3 4 6 7 Q2N2222

Q4 7 7 8 Q2N2222

Q5 6 7 8 Q2N2222

RX 1 6 2.26K

.MODEL Q2N2222 NPN (BF=191 IS=4E-15)

.LIB C:\PS8\LIB\BIPOLAR.LIB

.TRAN/OP 1.000U 4M 0 20U

.PROBE

\*\*\*\*\* 01/17/2000 03:53:35 \*\*\*\*\* NT Evaluation PSpice (July 1997) \*\*\*\*\*

## AMPLIFICADOR DIFERENCIAL CON ENTRADA Y SALIDA ASIMETRICA

### \*\*\*\* BJT MODEL PARAMETERS

\*\*\*\*\*

Q2N2222

NPN

IS 4.000000E-15

BF 191

NF 1

BR 1

NR 1

\*\*\*\*\* 01/17/2000 03:53:35 \*\*\*\*\* NT Evaluation PSpice (July 1997) \*\*\*\*\*

## AMPLIFICADOR DIFERENCIAL CON ENTRADA Y SALIDA ASIMETRICA

### \*\*\*\* INITIAL TRANSIENT SOLUTION TEMPERATURE = 27.000 DEG C

\*\*\*\*\*

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 12.0000 ( 2) 2.1854 ( 3) 0.0000 ( 4) -.7202

( 5) 2.1854 ( 6) -10.5240 ( 7) -11.2620 ( 8) -12.0000

### VOLTAGE SOURCE CURRENTS

NAME CURRENT

VCC -1.988E-02

VEE -1.993E-02

Vi -2.595E-05

TOTAL POWER DISSIPATION 4.78E-01 WATTS

-

\*\*\*\* 01/17/2000 03:53:35 \*\*\*\*\* NT Evaluation PSpice (July 1997) \*\*\*\*\*

AMPLIFICADOR DIFERENCIAL CON ENTRADA Y SALIDA ASIMETRICA

\*\*\*\* OPERATING POINT INFORMATION TEMPERATURE = 27.000 DEG C

\*\*\*\*\*

\*\*\*\* BIPOLAR JUNCTION TRANSISTORS

NAME Q1 Q2 Q3 Q4 Q5

MODEL Q2N2222 Q2N2222 Q2N2222 Q2N2222 Q2N2222

IB 2.60E-05 2.60E-05 5.22E-05 5.19E-05 5.19E-05

IC 4.96E-03 4.96E-03 9.97E-03 9.91E-03 9.91E-03

VBE 7.20E-01 7.20E-01 7.38E-01 7.38E-01 7.38E-01

VBC -2.19E+00 -2.19E+00 -9.80E+00 0.00E+00 -7.38E-01

VCE 2.91E+00 2.91E+00 1.05E+01 7.38E-01 1.48E+00

BETADC 1.91E+02 1.91E+02 1.91E+02 1.91E+02 1.91E+02

GM 1.92E-01 1.92E-01 3.85E-01 3.83E-01 3.83E-01

RPI 9.97E+02 9.97E+02 4.96E+02 4.98E+02 4.98E+02

RX 0.00E+00 0.00E+00 0.00E+00 0.00E+00 0.00E+00

RO 1.00E+12 1.00E+12 1.00E+12 8.66E+11 1.00E+12

CBE 0.00E+00 0.00E+00 0.00E+00 0.00E+00 0.00E+00

CBC 0.00E+00 0.00E+00 0.00E+00 0.00E+00 0.00E+00

CJS 0.00E+00 0.00E+00 0.00E+00 0.00E+00 0.00E+00

BETAAC 1.91E+02 1.91E+02 1.91E+02 1.91E+02 1.91E+02

CBX 0.00E+00 0.00E+00 0.00E+00 0.00E+00 0.00E+00

FT 3.05E+18 3.05E+18 6.13E+18 6.10E+18 6.10E+18

JOB CONCLUDED

TOTAL JOB TIME .29

-

#### **5.4. GRÁFICAS DE PSPICE PROBE.**

Gráfica de señal de entrada de la fuente de alterna V(3), esta señal se introduce en una de las base.

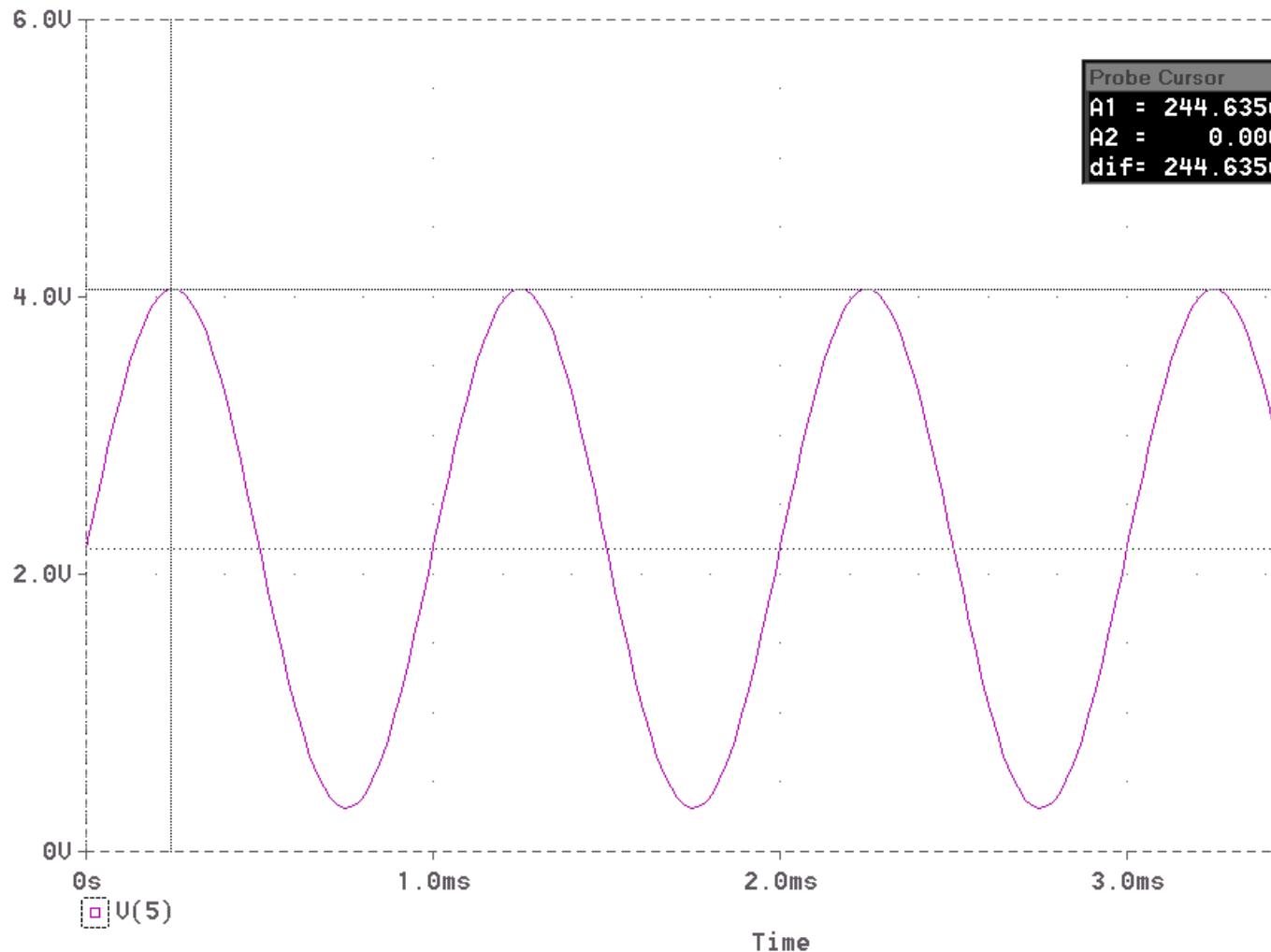

Gráfica de tensión de salida tomada en uno de los colectores V(5). Se observa que la señal de salida está en fase con señal de entrada.

## 6. DOCUMENTACIÓN TÉCNICA REFERENTE AL TRANSISTOR Q2N2222A

### 7. BIBLIOGRAFÍA.

Para el desarrollo y realización de la presente práctica nos hemos apoya en los siguientes textos:

- Dispositivos electrónico y Amplificación de señales.

Autor: Sedra y Smith.

- Microelectrónica.

Autor: Millman–Grabel

- Principios de Electrónica.

Autor: Malvino.